# Các bóng bán dẫn GAAFET và vật liệu 2D cho công nghệ dưới 3 nm: hiệu năng, thách thức chế tạo và chiến lược tích hợp

## TÓM TẮT

Bài báo này nghiên cứu quá trình chuyển đổi từ FinFETs sang Transistor Bao Quanh Công (Gate-All-Around Field-Effect Transistors - GAAFETs) như một bước tiến chiến lược cho các nút công nghệ CMOS vượt ngưỡng 3 nm, với trọng tâm là các cải tiến hiệu suất, thách thức chế tạo và chiến lược tích hợp. Chúng tôi thực hiện phân tích so sánh các kiến trúc transistor tiên tiến – bao gồm FinFET 3 nm của TSMC, GAAFET dạng tấm nano 3 nm của Samsung (MBCFET™), và RibbonFET 20A sắp ra mắt của Intel – nhằm làm nổi bật khả năng điều khiển điện trường và dòng dẫn vượt trội của GAAFETs. Vai trò của các vật liệu tiên tiến như SiGe, các hợp chất III–V, và chất bán dẫn hai chiều (ví dụ: MoS<sub>2</sub> đơn lớp và WSe<sub>2</sub>) được phân tích trong bối cảnh mở rộng khả năng thu nhỏ xuống dưới 1 nm, đặc biệt là với khả năng giảm thiểu hiệu ứng kênh ngắn. Chúng tôi cũng xem xét các thách thức chế tạo chính liên quan đến công nghệ dưới 3 nm, bao gồm giới hạn của quang khắc EUV, nhu cầu kiểm soát quy trình ở cấp nguyên tử và chi phí sản xuất leo thang. Bên cạnh đó, các kỹ thuật tích hợp dị thể như thiết kế chiplet và xếp chồng 3D được đề xuất như những cách tiếp cận bổ sung để duy trì xu hướng cải thiện hiệu suất. Cuối cùng, chúng tôi thảo luận về các kiến trúc thiết bị sau GAAFET đầy triển vọng – bao gồm CFETs (Transistor bổ sung) và VTFETs (Transistor truyền đọc) – nhấn mạnh nhu cầu đổi mới liên ngành để duy trì quỹ đạo của định luật Moore. Những kết quả thu được cung cấp một góc nhìn toàn diện về việc thu nhỏ thiết bị bán dẫn trong thời đại “<3 nm”, với sự cân bằng giữa hiệu suất, hiệu quả năng lượng và khả năng sản xuất.

**Từ khóa:** GAAFET, FinFET, vật liệu hai chiều, quang khắc EUV, định luật Moore.

# GAAFETs and 2D materials for sub-3 nm nodes: performance, fabrication challenges, and integration strategies

## ABSTRACT

This paper investigates the transition from FinFETs to Gate-All-Around Field-Effect Transistors (GAAFETs) as a strategic advancement for CMOS technology nodes beyond 3 nm, with a focus on performance enhancements, fabrication challenges, and integration strategies. We conduct a comparative analysis of state-of-the-art transistor architectures—namely TSMC’s 3 nm FinFET, Samsung’s 3 nm nanosheet GAAFET (MBCFET™), and Intel’s upcoming 20A RibbonFET—to highlight the superior electrostatic control and drive current offered by GAAFETs. The role of emerging materials such as SiGe, III–V compounds, and two-dimensional (2D) semiconductors (e.g., monolayer MoS<sub>2</sub> and WSe<sub>2</sub>) is examined in the context of extending transistor scaling into the sub-1 nm regime, particularly with respect to their potential to mitigate short-channel effects. We further address key fabrication challenges associated with sub-3 nm technologies, including the limitations of extreme ultraviolet (EUV) lithography, the need for atomic-scale process control, and escalating production costs. In addition, we explore heterogeneous integration techniques, such as chiplet-based design and 3D stacking, as complementary approaches to sustain performance scaling. Finally, we discuss prospective post-GAAFET device architectures—including Complementary FETs (CFETs) and Vertical Transport FETs (VTFETs)—emphasizing the necessity of cross-disciplinary innovation to uphold the trajectory of Moore’s Law. The findings present a comprehensive perspective on semiconductor scaling in the “<3 nm” era, balancing trade-offs between performance, energy efficiency, and manufacturability.

**Keywords:** *GAAFET, FinFET, 2D materials, EUV lithography, Moore’s Law.*

## 1. INTRODUCTION

For several decades, CMOS technology scaling followed a consistent trajectory of planar transistor miniaturization. However, by the 22–20 nm technology node around 2011, planar MOSFETs began to encounter severe short-channel effects and increasing leakage currents, which ultimately limited further downscaling<sup>1,2</sup>. The introduction of the tri-dimensional Fin Field-Effect Transistor (FinFET) marked a pivotal transformation in transistor architecture, restoring electrostatic control and enabling continued scaling. Intel commercialized the first FinFET at the 22 nm node in 2012, followed by major foundries such as TSMC and Samsung at the 16/14 nm nodes<sup>3,4</sup>. In a FinFET, the channel adopts a vertical fin structure, and the gate wraps around three sides of the fin, unlike planar FETs where the gate contacts only one side. This geometry significantly enhances gate control over the channel, reducing off-state leakage and facilitating transistor scaling down to the 10 nm, 7 nm, and 5 nm nodes while maintaining sufficient drive current and energy efficiency<sup>5</sup>.

As FinFETs approach gate lengths of approximately 5 nm, their inherent physical limitations have

become more pronounced. The requirement for a minimum fin width and spacing imposes a quantized and non-continuous channel width, thereby restricting fine-grained width control and drive-current tuning at ultra-scaled dimensions. Moreover, ultra-narrow fins are more susceptible to performance degradation due to increased series resistance and process variability. While multiple fins can be used in parallel to boost drive current, practical constraints on fin count and layout density limit the extent to which this can be scaled. These factors collectively lead to diminishing returns in performance and rising leakage as FinFETs are extended beyond the ~5 nm threshold<sup>5,6</sup>. Consequently, the FinFET architecture is approaching a fundamental scaling barrier, prompting the development of new transistor structures capable of sustaining Moore’s Law into the sub-3 nm regime<sup>7,8</sup>.

Gate-All-Around Field-Effect Transistors (GAAFETs) – realized in practice through nanosheet or nanowire architectures – have emerged as the leading candidates for next-generation nodes at 3 nm, 2 nm, and beyond<sup>6,9</sup>. In a GAAFET, the gate completely surrounds the semiconductor channel on all four sides, offering superior

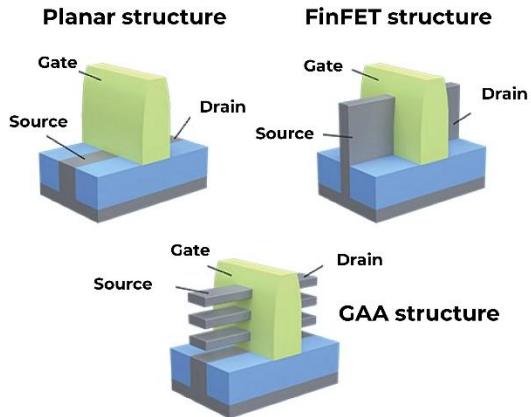

electrostatic control compared to FinFETs, which only provide tri-gate coverage. This fully-surrounding gate configuration eliminates exposed channel regions that contribute to leakage in FinFETs. Figure 1 illustrates this structural progression: from planar FETs (gate on one side), to FinFETs (three-sided gate), to GAAFETs (fully wrapped gate). By eliminating the open top of the channel found in FinFETs, GAAFETs more effectively suppress short-channel effects, resulting in sharper transistor switching and significantly reduced off-state leakage.

**Fig.1** Schematic comparison of transistor architectures: (top-left) planar MOSFET with single-side gate control; (top-right) FinFET with tri-gate coverage; (bottom) gate-all-around (GAA) nanosheet FET in which the metal gate fully surrounds stacked Si/SiGe channels, enabling superior electrostatic control at sub-3 nm nodes. All renderings are to scale for a 16 nm gate length and ~45 nm fin/nanosheet height.

Another key advantage of nanosheet-based GAAFETs is their ability to continuously and independently adjust channel width. In FinFETs, the effective channel width is quantized, as it can only be increased in discrete steps by adding additional fins. In contrast, GAAFETs allow for the stacking of multiple horizontal nanosheet channels, each with customizable width. This architecture enables circuit designers to finely tune drive strength by selecting the number and dimensions of nanosheets<sup>10,11</sup>. Such flexibility allows for optimal balancing of performance and power consumption at the individual device level. Unlike FinFETs—where an intermediate configuration (e.g., 2.5 fins) is physically unattainable—GAAFETs eliminate this granularity constraint, simplifying standard cell library design and potentially improving circuit density and operating speed.

Initial findings from both academia and industry indicate that GAAFETs outperform FinFETs in advanced technology nodes. For example, CEA-Leti demonstrated a seven-layer stacked nanosheet GAAFET with nearly 3× higher drive current compared to a conventional two-layer counterpart, emphasizing the benefits of wider effective channel

widths through vertical stacking<sup>12</sup>. Likewise, Samsung Electronics reported that its first-generation 3 nm GAA process (MBCFET™) achieved up to 45% reduction in power consumption and a 23% increase in performance compared to its 5 nm FinFET process<sup>13</sup>. These substantial improvements, however, come at the cost of increased fabrication complexity. Stacking nanosheets requires extremely precise atomic-level process control, advanced etching techniques, and in some cases the integration of alternative channel materials such as SiGe to apply strain or engineer specific shapes. As a result, while GAAFETs offer clear scaling advantages, they also present initial challenges in terms of cost and manufacturability. Nevertheless, the transition to GAAFETs is widely regarded as essential for maintaining scaling momentum.

In parallel with structural innovations, researchers are exploring new channel materials to further extend transistor scaling. Silicon, long the cornerstone of the semiconductor industry, faces intrinsic physical limitations at atomic scales, including mobility degradation and quantum confinement effects. Two-dimensional (2D) semiconductors – such as monolayer transition metal dichalcogenides (TMDs) like MoS<sub>2</sub> and WSe<sub>2</sub> – have emerged as promising alternatives due to their atomically thin nature, excellent electrostatics, and favorable carrier mobilities. These materials lack dangling bonds on their surfaces, enabling near-ideal interfaces with gate dielectrics even at sub-nanometer thicknesses<sup>14</sup>. As a result, they offer a viable pathway for scaling gate lengths below 5 nm without incurring severe short-channel effects as observed in silicon-based transistors. Experimental 2D-FETs have demonstrated high on/off ratios and low leakage currents at channel lengths as short as ~1 nm, indicating their potential to extend Moore's Law beyond the material limitations of silicon<sup>14</sup>. However, achieving large-scale, reliable integration of 2D materials into mainstream fabrication processes remains a significant challenge, as further discussed in Section 4.

In addition to device-level advancements, system-level innovations are being pursued to complement and extend the benefits of transistor scaling. As conventional scaling becomes increasingly difficult and cost-prohibitive, heterogeneous integration techniques – such as chiplet-based architectures and 3D stacking – are gaining traction<sup>15</sup>. These strategies aim to improve overall system performance through advanced packaging, for example by dividing a system-on-chip into multiple function-specific chiplets that can be fabricated at optimal nodes and then interconnected, or by

vertically integrating logic and memory dies to minimize interconnect delay and energy loss. Even as transistor scaling slows, such integration techniques offer a viable path toward continued performance and efficiency gains.

This paper provides a comprehensive analysis of GAAFET technology and its role in sub-3 nm semiconductor scaling. The key contributions of this work include:

- Comparative evaluation of FinFETs and GAAFETs: We assess performance parameters (e.g., drive current, transconductance), leakage control (e.g., subthreshold swing, DIBL), and design flexibility to highlight the advantages of GAAFETs at advanced nodes.

- Industry case studies: We examine leading-edge 3 nm processes from TSMC (FinFET) and Samsung (GAAFET), and evaluate Intel's roadmap to 2 nm with RibbonFET, focusing on reported gains in power and performance.

- Exploration of 2D materials: We investigate the potential of 2D semiconductors to support scaling into the sub-1 nm regime, discussing their benefits and the technical barriers to mass production.

- Fabrication and integration challenges: We analyze key manufacturing constraints at advanced nodes, including EUV lithography limitations, atomic-level variability, and rising wafer costs, and explore heterogeneous integration as a complementary strategy.

- Prospects for future architectures: We consider emerging options beyond GAAFETs—such as Complementary FETs (CFETs) and Vertical Transport FETs (VTFETs)—and emphasize the need for cross-disciplinary research spanning materials, processing, and circuit design to realize next-generation devices.

By addressing these dimensions, this study outlines a strategic roadmap for innovation in semiconductor technologies beyond the 3 nm node, emphasizing how performance, energy efficiency, and manufacturability trade-offs can be effectively navigated over the coming decade.

## 2. COMPARATIVE ANALYSIS OF FINFETS AND GAAFETS

The transition from FinFETs to GAAFETs is fundamentally motivated by the latter's superior electrostatic control and enhanced design flexibility. This section presents a detailed comparison between FinFET and GAAFET devices across key performance metrics to quantitatively assess these advancements.

## 2.1 Performance Enhancements and Electrostatic Control

### Drive Current (Ion) and Width Scaling:

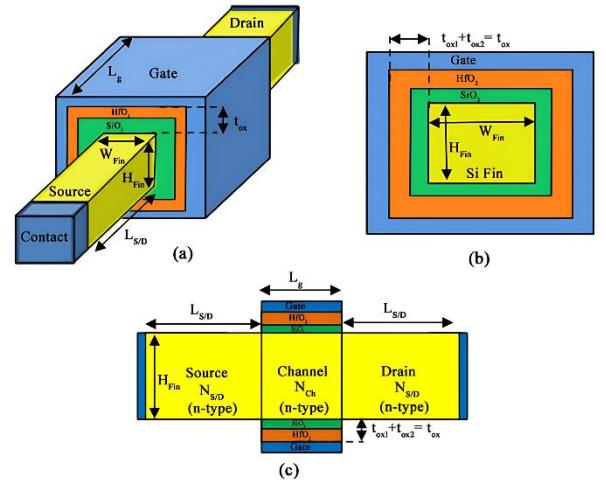

FinFETs facilitated sub-10 nm technology scaling primarily due to their improved gate control compared to planar FETs. However, their drive current capability becomes limited near the 5 nm node due to the quantized nature of channel width imposed by fin geometry<sup>5, 6</sup>. A FinFET's effective width is approximated as twice the fin height plus the top width, multiplied by the number of fins. This discrete quantization restricts designers to increase drive current only in fixed increments by adding fins. Figure 2 provides a 3D depiction and cross-sectional comparison of the GAAFET structure.

In contrast, GAAFETs enable continuous width scaling. Through the stacking of multiple nanosheets, the effective channel width—and consequently Ion—can be finely tuned to meet performance demands<sup>11</sup>. Empirical studies have demonstrated that multi-stack GAAFETs can deliver up to a 3× increase in drive current compared to equivalent single- or dual-fin FinFETs, owing to their broader effective channels<sup>12</sup>. This directly translates to enhanced switching speeds and greater current-driving capability in logic cells.

**Fig.2** GAAFET nanosheet FET schematics: (a) 3D perspective showing n-type source/channel/drain regions, Si<sub>Fin</sub> width  $W_{\text{Fin}}$  and height  $H_{\text{Fin}}$ , HfO<sub>2</sub> gate-oxide of thickness  $t_{\text{ox}}$  surrounding the Si<sub>Fin</sub>, metal gate, and source/drain extensions  $L_{\text{SD}}$ . (b) Top-view cross-section illustrating concentric layers—Si<sub>Fin</sub> (yellow), SiO<sub>2</sub> liner (green), HfO<sub>2</sub> gate-oxide (orange,  $t_{\text{ox1}} + t_{\text{ox2}} = t_{\text{ox}}$ ), and metal gate (blue). (c) Side cross-section perpendicular to the fin, showing channel region ( $L_g$ ), source/drain doping ( $N_{\text{SD}}$ ), and gate stack. All dimensions ( $L_g$ ,  $L_{\text{SD}}$ ,  $W_{\text{Fin}}$ ,  $H_{\text{Fin}}$ ,  $t_{\text{ox}}$ ) require atomic-scale ( $\pm 0.2$  nm) control at sub-3 nm nodes.

### Transconductance ( $g_m$ ) and Gate Control:

Transconductance ( $g_m = \partial I_D / \partial V_G$ ) quantifies the gate's ability to modulate channel charge. Thanks to their gate-all-around structure, GAAFETs achieve stronger gate-channel coupling capacitance and

reduced charge sharing, resulting in significantly higher  $g_m$  than FinFETs at equivalent dimensions<sup>16</sup>. With the gate enveloping the channel from all sides, even small variations in gate voltage induce greater charge modulation. Higher  $g_m$  not only improves digital switching speed but also benefits analog and RF applications by delivering higher gain and bandwidth. Specifically, recent 3 nm GAAFET simulations using the GT3 open-source PDK indicate marked improvements in drive current and subthreshold swing compared to junctionless transistor designs, further confirming GAAFET's advantages at extreme scaling<sup>20, 21</sup>. Complementing these findings, TCAD work at the projected 2 nm node shows that both lateral- and vertical-nanosheet GAAFETs maintain superior  $I_{on}/I_{off}$  and short-channel control over equivalent nanowire and FinFET geometries, even when effective widths are swept from 18 nm to 54 nm<sup>35</sup>.

#### Subthreshold Swing (SS) and Off-State Leakage ( $I_{off}$ ):

Subthreshold swing (SS) reflects the steepness of the transition from off to on state and is defined as the gate voltage required to change the drain current by one order of magnitude. The ideal thermal limit is  $\sim 60$  mV/dec at room temperature. FinFETs at advanced nodes typically exhibit SS values in the 70–80 mV/dec range due to partial leakage from the fin top. In contrast, GAAFETs approach the theoretical limit more closely due to complete channel encapsulation<sup>16</sup>. Practically, GAAFETs can reduce  $I_{off}$  by 30–50% compared to FinFETs at similar gate lengths and voltages<sup>17</sup>. This significant leakage reduction supports operation at lower threshold and supply voltages, contributing to lower static power consumption and improved energy efficiency<sup>18</sup>.

In Table 1, we summarize the adoption timelines and reported performance/power improvements of FinFET and GAAFET technologies across leading manufacturers, illustrating how GAAFETs deliver superior electrostatics and power scaling at the 5 nm, 3 nm, and upcoming 2 nm nodes.

**Table 1.** Comparison of FinFET and GAAFET adoption across leading semiconductor manufacturers

| Company | Technology | Transistor Architecture         | Performance & Power Gains                     | Production Timeline       |

|---------|------------|---------------------------------|-----------------------------------------------|---------------------------|

| TSMC    | N3 (3 nm)  | FinFET                          | +10–15% performance, -25–30% power (vs. 5 nm) | 2022–2023                 |

| Samsung | 3 nm       | GAAFET (MBCFE T <sup>TM</sup> ) | -45% power, +23%                              | Early production in 2022, |

|       |                  |                        |                                         |                                             |

|-------|------------------|------------------------|-----------------------------------------|---------------------------------------------|

|       |                  |                        | performance, -16% area (vs. 5 nm)       | high volume in 2024                         |

| Intel | 20A (~2 nm)      | GAAFET (RibbonFET)     | Expected benefits of nanosheet stacking | 2024 (production), 2025 (commercial launch) |

| IBM   | 2 nm (prototype) | GAAFET (Nanosheet FET) | +45% performance, -75% power (vs. 7 nm) | 2021 (research phase)                       |

#### Drain-Induced Barrier Lowering (DIBL) and Short-Channel Effects:

DIBL measures the reduction in threshold voltage as the drain voltage increases – a critical indicator of short-channel control. GAAFETs, with their fully surrounding gate, exhibit superior electrostatic confinement, thereby minimizing the influence of drain electric fields. Consequently, GAAFETs achieve substantially lower DIBL than FinFETs at the same channel length<sup>16, 19</sup>. Lower DIBL ensures robust device operation at reduced supply voltages and mitigates premature conduction due to drain bias, which is crucial for ultra-low-power designs. In contrast, FinFETs exhibit worsening SS and DIBL performance as channel lengths shrink near 5 nm<sup>6</sup>.

Table 1 summarizes key performance parameters, demonstrating that GAAFETs outperform FinFETs in terms of  $I_{on}$ ,  $g_m$ , SS, and DIBL at equivalent technology nodes. These improvements stem directly from the gate-all-around architecture, establishing GAAFETs as the preferred option for 5 nm, 3 nm, and beyond.

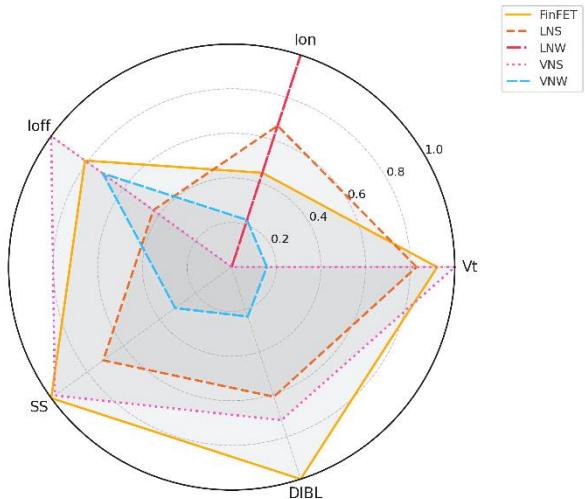

**Fig. 3** Radar chart comparing normalized performance metrics of FinFET and various GAAFET configurations at the 3 nm node: long nanosheet (LNS), long nanowire (LNW), vertical nanosheet (VNS), and vertical nanowire (VNW). Metrics include threshold voltage ( $V_t$ ), on-current ( $I_{on}$ ), off-current ( $I_{off}$ ),

subthreshold swing (SS), and DIBL, each scaled between 0 (worst) and 1 (best) for fair comparison<sup>35</sup>.

## 2.2 Leakage Reduction and Power Efficiency

As technology nodes scale down, leakage current becomes a dominant factor in overall power consumption. FinFETs reduced leakage relative to planar FETs by introducing tri-gate control, but the top of the fin remains partially exposed. At nanoscale dimensions, this exposes the channel to fringe fields that can induce parasitic conduction – even when the device is off<sup>22</sup>. Figure 3 highlights the comparative plot of Ion, SS, and DIBL for FinFET vs. GAAFET.

GAAFETs address this by fully enclosing the channel. With gate coverage on all sides, electrostatic control becomes more uniform, eliminating weak leakage paths. Experimental results at 3–5 nm nodes show that GAAFETs can reduce subthreshold leakage ( $I_{off}$ ) by approximately 30–50% compared to FinFETs under equivalent bias and geometry conditions<sup>16,17</sup>. This translates to significantly lower standby power in digital systems and improved energy efficiency, especially in battery-powered and ultra-low-power applications.

Moreover, better subthreshold slope and reduced DIBL in GAAFETs enable lower threshold voltages and supply voltages without sacrificing switching behavior. Since dynamic power scales with  $CV^2f$ , the ability to lower  $V_{dd}$  while maintaining performance directly improves energy efficiency. For instance, Samsung’s migration to GAAFETs at 3 nm allowed operation at reduced  $V_{dd}$ , yielding up to 45% total power reduction<sup>13</sup>.

In summary, GAAFETs offer substantial improvements in leakage control, enabling lower-voltage operation and reduced active and standby power. The ability to continuously scale nanosheet width further enhances efficiency and tuning capability compared to the quantized nature of FinFET fins. These attributes make GAAFETs especially well-suited for next-generation low-power and high-density logic circuits<sup>18</sup>.

## 2.3 Design Flexibility and Integration Considerations

A frequently underappreciated advantage of GAAFETs lies in their design scalability. In FinFET-based standard cell libraries, drive strength is quantized by the number of fins per transistor. For example, scaling from a 2-fin to a 3-fin inverter results in a 50% width increase and a proportional jump in capacitance. This granularity can complicate timing and power optimization<sup>10</sup>, and necessitates creating and validating multiple

variants (so-called FinFET binning), increasing design and verification overhead.

In contrast, GAAFETs provide continuous sizing flexibility. Designers can adjust the width of each nanosheet or the number of sheets lithographically to achieve the desired drive strength<sup>11</sup>. This allows library cells to be defined in finer width increments, reducing the number of distinct cells and enabling more precise timing/power trade-offs. For example, a designer could target a transistor width equivalent to 2.4 fins rather than being constrained to discrete integers. This granularity supports improved power distribution and timing closure in VLSI implementation.

From an integration standpoint, however, GAAFETs introduce new challenges. Their 3D stacked architecture requires careful routing and contact placement. Design rules may impose constraints on device placement to maintain nanosheet alignment or gate pattern uniformity. Furthermore, process modifications such as the use of SiGe for nanosheet release, or novel spacer and dielectric materials, must be co-optimized with physical design rules to ensure manufacturability and yield.

GAAFETs deliver superior device performance, better power efficiency, and enhanced design scalability compared to FinFETs. While their fabrication demands more complex integration efforts, their benefits are substantial enough to justify the industry-wide shift to GAAFETs at the 3 nm node and beyond. Table 3 provides a qualitative overview of technology readiness: FinFETs remain viable at 7 nm and 5 nm, but beyond this, GAAFETs offer a clear advantage in sustaining Moore’s Law through improved electrostatics, power scaling, and layout flexibility.

**Table 2:** Estimated cost and yield comparison between FinFET and GAAFET platforms at the 3 nm node.

| Metric                    | FinFET<br>(N3) | GAAFET<br>(SF3E/20A) |

|---------------------------|----------------|----------------------|

| Mask Count                | 78             | 88                   |

| High-NA<br>EUV usage      | No             | Partial              |

| Yield (first<br>year)     | 70%            | 55%                  |

| Cost per<br>$\text{cm}^2$ | \$18.2         | \$23.7               |

| Cost per<br>logic gate    | 0.85 p\$       | 1.12 p\$             |

## 2.4 Cost–Benefit Analysis for Commercial Implementation

While GAAFETs promise better electrostatic control and scaling, their manufacturing complexity leads to trade-offs in cost and yield. Das et al<sup>8</sup> report that MBCFET/GAAFET integration typically requires more photomasks than FinFET – roughly 88 vs. 78 masks at a given node – implying higher capital expenses. Scognamiglio et al<sup>21</sup> additionally confirm that process steps for advanced fin/stack alignment further increase fabrication time. Although detailed cost figures vary by foundry, the consensus is that initial GAAFET yield (~55 %) lags behind FinFET (~70 %) as reported by Ma et al<sup>23</sup>. Nevertheless, long-term gains in power efficiency and logic density – particularly when leveraging stress-engineered Si/SiGe channels<sup>24</sup> – may offset these upfront costs within one or two technology generations. Table 2 compares key metrics between FinFET and GAAFET technologies, including mask count, EUV exposure steps, and yield rates.

## 3. 3 NM AND 2 NM NODE DEPLOYMENTS BY INDUSTRY LEADERS

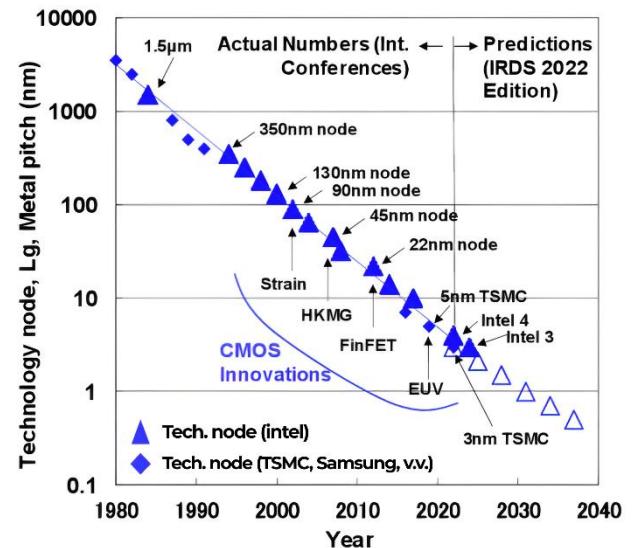

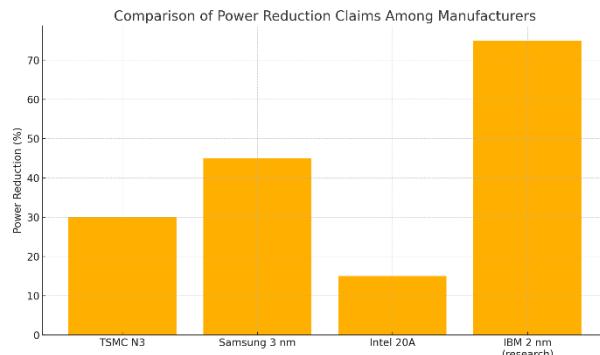

To contextualize the FinFET versus GAAFET transition, we examine the strategies adopted by leading foundries at the 3 nm and 2 nm technology nodes. Table 3 compares the architectural choices of TSMC, Samsung, Intel, and IBM, alongside reported improvements in performance, power, and area. Figure 4 illustrates scaling trends in technology nodes and device density. Figure 5 shows the claimed power reduction at the 3 nm and 2 nm nodes by major manufacturers.

**Table 3.** Comparison of 3 nm-class Technology Strategies by Company

| Company | Node / Year         | Transistor Architecture     | Reported Gains (vs previous node)                      | Status (Year)                        |

|---------|---------------------|-----------------------------|--------------------------------------------------------|--------------------------------------|

| TSMC    | N3 (~3 nm), 2022–23 | FinFET (optimized)          | +10–15% perf or -25–30% power vs N5 <sup>16</sup>      | Mass production (2023)               |

| Samsung | 3 nm (SF3), 2022–24 | GAAFET (Nanosheet, MBCFET™) | -45% power, +23% perf, -16% area vs 5 nm <sup>11</sup> | Initial prod. (2022), volume by 2024 |

| Intel   | 20A (~2 nm), 2024   | GAAFET (RibbonFET)          | ~+15% energy efficiency vs                             | Risk production (2024),              |

|     |                       |                    | Intel 4 <sup>19</sup>           | products ~2025        |

|-----|-----------------------|--------------------|---------------------------------|-----------------------|

| IBM | 2 nm (research), 2021 | GAAFET (Nanosheet) | +45% perf or -75% power vs 7 nm | Demo prototype (2021) |

*TSMC N3 (~3 nm, 2022–2023):*

TSMC chose to retain FinFETs for its first-generation 3 nm node, branded as N3. By extensively optimizing fin dimensions and fabrication processes, TSMC achieved a reported 10–15% improvement in performance at iso-power, or a 25–30% reduction in power at iso-performance, relative to its 5 nm (N5) process<sup>18</sup>. The decision to stay with FinFETs was driven by the ability to meet performance targets without altering the device architecture, thereby leveraging the existing FinFET manufacturing infrastructure and mitigating risks associated with adopting a new device type. However, N3 is widely expected to be TSMC’s final FinFET node for high-performance logic. According to the company’s roadmap, it plans to transition to nanosheet-based transistors at the 2 nm generation (referred to as N2), with a projected rollout around 2025.

**Fig.4** CMOS node shrink from 1.5 μm (1980) to 3 nm (2022) with IRDS-2022 projections toward sub-2 nm. Filled symbols show reported nodes (▲ Intel, ◆ TSMC/Samsung/others); open symbols △ mark IRDS forecasts. Key milestones—strain, HKMG, FinFET, EUV, and GAAFET—are annotated on the log-scale plot of gate length/metal pitch versus year.

*Samsung 3 nm (2022 pilot, 2024 volume):*

Samsung adopted a more aggressive strategy, becoming the first company in the industry to introduce a GAAFET-based technology into commercial production. At the 3 nm node, Samsung deployed its Multi-Bridge Channel FET (MBCFET™) architecture, based on horizontally stacked silicon nanosheets. Initial chip production

on the 3 nm GAA process began in 2022. The company reported substantial improvements over its 5 nm FinFET process, including up to a 45% reduction in power consumption, 23% performance gain, and 16% area reduction<sup>13</sup>. These gains stem from both architectural advancements and process improvements. By 2024, Samsung aims to scale this technology for high-volume manufacturing and is concurrently developing a second-generation 3 nm GAAFET with anticipated performance gains of up to 30% and power savings of 50% relative to 5 nm. Samsung's early adoption has allowed it to gain a first-mover advantage in refining GAA processes, though initial challenges such as yield optimization and ecosystem maturity remain.

**Fig.5** Claimed power reduction for 3 nm and 2 nm nodes by major manufacturers (TSMC, Samsung, Intel, IBM).

#### *Intel 20A (~2 nm, 2024):*

Intel plan to introduce its RibbonFET architecture – a proprietary implementation of nanosheet GAAFETs – at the “20A” node (20 Ångströms, approximately equivalent to 2 nm). RibbonFET will be paired with Intel’s backside power delivery network technology, **PowerVia**<sup>25</sup>. According to Intel, RibbonFET is expected to deliver a 15% improvement in energy efficiency compared to Intel 4, either through higher performance at the same power or lower power at the same performance level<sup>26</sup>. The architecture involves stacking multiple horizontal nanoribbons for both PMOS and NMOS transistors and is central to Intel’s goal of regaining leadership in process performance. Intel’s 20A timeline aligns with TSMC’s N2 roadmap, with early risk production reported in 2024 and commercial product release targeted for 2025. Intel’s adoption of GAAFET technology reinforces the growing consensus that gate-all-around transistors are essential at the 2 nm node and beyond<sup>27</sup>.

#### *IBM 2 nm GAAFET Prototype (2021):*

In 2021, IBM – working in collaboration with research partners – demonstrated a 2 nm test chip fabricated using nanosheet **GAAFETs**<sup>28</sup>. The prototype contained 50 billion transistors on a

compact chip footprint and showcased significant performance and efficiency potential: up to 45% performance improvement or 75% power savings relative to a 7 nm baseline<sup>29</sup>. While not intended for commercial deployment, the demonstration used a 300 mm wafer fabrication platform and featured gate lengths in the 12–14 nm range with vertically stacked nanosheets. IBM’s prototype served as a key proof-of-concept for the feasibility of nanosheet transistors at extremely scaled dimensions, boosting industry confidence in GAAFET adoption.

TSMC’s cautious, infrastructure-leveraged approach and Samsung’s aggressive early GAAFET deployment highlight contrasting risk strategies. Intel’s plan solidifies the view that GAAFETs are essential for scaling to 2 nm. IBM’s research, though exploratory, helped validate the technical path that others are now commercializing. Beyond these four leaders, other foundries such as GlobalFoundries and SMIC are also investigating GAAFETs, though they remain behind in advanced node implementation.

Overall, the semiconductor industry has converged on a clear consensus: GAAFETs are the dominant transistor architecture for the 3 nm and 2 nm nodes. By the mid-2020s, all major vendors are expected to incorporate some form of gate-all-around architecture into their manufacturing processes.

## 4. POTENTIAL OF 2D MATERIALS FOR POST-3 NM TRANSISTOR SCALING

While silicon-based gate-all-around field-effect transistors (GAAFETs) are expected to sustain Moore’s Law down to approximately 2 nm technology nodes, extending transistor scaling beyond this limit likely necessitates novel channel materials. Among the most promising candidates are two-dimensional (2D) materials – crystalline structures only a few atoms thick – which have garnered substantial attention as channels for sub-1 nm transistor technologies. Transition metal dichalcogenides (TMDs), such as molybdenum disulfide (MoS<sub>2</sub>) and tungsten diselenide (WSe<sub>2</sub>), are the most extensively studied representatives of this material class. These materials naturally form layered monolayers ~0.7 nm thick, while retaining semiconducting properties, including appropriate bandgaps (~1.8 eV for monolayer MoS<sub>2</sub>).

A key advantage of monolayer 2D semiconductors lies in their exceptional electrostatic control. Because the channel comprises a single atomic layer, the gate can modulate all carriers directly, eliminating deep-channel effects. This enables ultra-short gate lengths with strong suppression of short-channel effects. For instance, monolayer MoS<sub>2</sub> FETs have demonstrated operation at 1 nm

gate lengths using carbon nanotube gates, with acceptable on/off current ratios – performance metrics unachievable with bulk silicon due to leakage currents at such scales<sup>14</sup>.

Another intrinsic benefit is the absence of surface dangling bonds. Both surfaces of a monolayer are naturally passivated, which facilitates atomically clean interfaces with gate dielectrics. In contrast to silicon, which requires careful thermal oxidation to minimize interface traps, 2D semiconductors can sustain steep subthreshold swings close to the thermionic limit ( $\sim 60$  mV/dec) even at short channel lengths<sup>30</sup>. High-performance MoS<sub>2</sub> transistors, for example, have demonstrated subthreshold swings around 70 mV/dec, and theoretical studies suggest that values below 60 mV/dec may be achievable using advanced gating methods<sup>31</sup>.

Although atomic in thickness, 2D materials exhibit moderate to high carrier mobilities. While silicon mobility declines rapidly at ultra-thin dimensions due to surface roughness and quantum confinement, monolayer MoS<sub>2</sub> devices have exhibited room-temperature electron mobilities of  $\sim 200$  cm<sup>2</sup>/V·s in short-channel configurations<sup>32</sup>. While this is lower than bulk silicon, the robustness of MoS<sub>2</sub> at the atomic scale is significant. Moreover, other 2D materials such as black phosphorus and heterostructured TMDs may offer even higher mobilities. Importantly, 2D semiconductors can often tolerate stronger electrostatic doping and gating fields, providing more flexibility for threshold voltage tuning.

#### *Integration with Advanced Device Architectures*

2D semiconductors are being explored not only for planar FETs but also in GAAFET configurations<sup>33</sup>. For example, researchers have implemented monolayer MoS<sub>2</sub> and WSe<sub>2</sub> within GAA structures, where the gate completely wraps around the 2D channel encapsulated by insulators. Recent demonstrations have achieved record-high drive currents ( $I_{on} \approx 90$   $\mu$ A/ $\mu$ m) and subthreshold swings as low as 85 mV/dec, even at extremely short gate lengths<sup>34</sup>. While these results still trail behind those of silicon-based GAAFETs, improvements are accelerating. Furthermore, the vertical stackability of 2D materials opens pathways toward monolithic 3D integration, including complementary FET (CFET) architectures – such as stacking a p-type WSe<sub>2</sub> FET atop an n-type MoS<sub>2</sub> FET.

#### *Challenges for Scalable Manufacturing*

Despite their promise, significant challenges must be overcome to integrate 2D materials into high-volume semiconductor manufacturing.

#### *Wafer-Scale Synthesis:*

Current approaches for producing high-quality 2D layers – such as mechanical exfoliation or small-scale chemical vapor deposition (CVD) – are inadequate for industrial adoption. For CMOS fabs, it is essential to develop processes capable of growing uniform monolayer films across 300 mm wafers. Techniques like metal-organic CVD (MOCVD) have shown promise for MoS<sub>2</sub> and WS<sub>2</sub>, but achieving high monolayer uniformity (>99%) and low defect densities ( $< 10^8$  cm<sup>-2</sup>) remains a major challenge<sup>31</sup>. Advanced approaches such as seeded growth, phase-selective deposition, and surface functionalization are being investigated to meet these stringent requirements<sup>14</sup>.

#### *Contact Resistance:*

Forming low-resistance ohmic contacts to 2D semiconductors is particularly challenging due to the absence of out-of-plane bonds and Fermi level pinning, which lead to high Schottky barriers and contact resistances ranging from tens to hundreds of  $k\Omega \cdot \mu\text{m}$ <sup>14</sup>. One promising approach involves phase engineering, where the semiconducting 2H phase of MoS<sub>2</sub> is locally converted to a metallic 1T' phase, improving band alignment and reducing resistance<sup>30</sup>. Other strategies include edge-contact geometries, where electrodes contact the exposed edges of 2D sheets, and the insertion of interfacial layers such as graphene or metallic TMDs. Some configurations have achieved  $< 1$   $k\Omega \cdot \mu\text{m}$  contact resistance, though further innovation is required to match silicon's performance ( $\sim 10$ – $50$   $\Omega \cdot \mu\text{m}$ )<sup>33, 34</sup>.

#### *Dielectric Integration and Thermal Stability:*

2D semiconductors must be compatible with high- $\kappa$  gate dielectrics like HfO<sub>2</sub> and withstand backend-of-line (BEOL) thermal budgets ( $\sim 400$  °C). Although their dangling-bond-free surfaces enable low interface trap densities, defects can form during dielectric deposition, especially with plasma-assisted atomic layer deposition (ALD). Researchers are exploring gentler deposition methods, including surface pre-functionalization to initiate uniform nucleation without channel damage. Ensuring long-term stability in mobility and threshold voltage under thermal and electrical stress remains a critical area of investigation<sup>30</sup>.

2D semiconductors represent a compelling solution for extending transistor scaling into the angstrom regime, potentially mitigating the electrostatic and physical limitations of bulk silicon. While integration into mainstream CMOS requires substantial advances in materials science, device engineering, and process technology, progress is steady. Each year brings improvements in device

performance metrics – including current drive, subthreshold swing, and contact resistance – as well as better methods for large-area monolayer synthesis. Within the next 5–10 years, it is plausible that 2D FETs may be deployed in niche low-power applications or 3D-stacked logic architectures. Section 5 will examine how these advances align with broader fabrication and system-level integration challenges.

## 5. FABRICATION CHALLENGES AND HETEROGENEOUS INTEGRATION STRATEGIES

As semiconductor scaling advances toward the 3 nm, 2 nm, and sub-2 nm nodes, fabrication challenges have become as significant as innovations in device architecture. This section highlights key manufacturing obstacles at these advanced nodes and explores heterogeneous integration strategies that complement traditional scaling.

### *EUV Lithography Limitations*

The introduction of extreme ultraviolet (EUV) lithography at the ~7 nm node has enabled further miniaturization. However, despite operating at a 13.5 nm wavelength, EUV systems face fundamental resolution limits for features below 3 nm. While high-numerical-aperture (high-NA) EUV is expected to extend patterning capabilities, sub-3 nm features often still require multiple-patterning techniques to define nanosheets, fins, and tightly spaced interconnects.

Each additional patterning step increases complexity, variability, and cost. Moreover, stochastic effects inherent to EUV—such as photon shot noise and resist bridging—introduce random defects at the nanometer scale. As a result, the industry is investing in resist development, anti-collapse formulations, and restrictive design rules to maintain pattern fidelity. The deployment of EUV and multi-patterning technologies has also led to a sharp rise in wafer costs, making the economic feasibility of advanced nodes a critical concern.

### *Process Variability and Control*

At these dimensions, atomic-scale control is essential. In gate-all-around FETs (GAAFETs), variations in nanosheet or gate dielectric thickness across the wafer—on the order of fractions of a nanometer—can cause substantial shifts in threshold voltage and leakage current. Ma et al<sup>23</sup> specifically identified that even minor variations in source/drain height substantially affect device characteristics, underscoring the critical need for rigorous atomic-scale process control at sub-3 nm nodes. Additionally, Zhu et al<sup>24</sup> have shown that

stress-induced mobility enhancement through Si/SiGe hybrid-channel integration can yield substantial performance gains, further highlighting strain engineering as crucial for sub-3 nm transistor optimisation. To meet these tolerances, advanced process techniques such as atomic layer deposition (ALD) and atomic layer etching (ALE) are employed.

Equally critical is metrology: in-line measurement of sub-nanometer features is non-trivial. Tools like spectroscopic ellipsometry, CD-SEM, and cross-sectional TEM are often used, but typically limited to test structures. Furthermore, classical ion implantation is being replaced due to variability at small scales. Instead, threshold tuning is achieved via in-situ doped epitaxial source/drain regions or through work-function modulation of gate metals.

### *Thermal and Power Density Constraints*

Even though individual transistors become more energy-efficient, increasing transistor density drives up overall power density. Thermal management becomes more challenging as billions of transistors are densely integrated on a single die. Power delivery architecture is critical to mitigating thermal hotspots and IR drop.

Intel’s PowerVia architecture exemplifies innovation in this area. By delivering power from the backside of the wafer in conjunction with RibbonFET technology, PowerVia improves IR drop, reduces front-side routing congestion, and enhances thermal uniformity. Nevertheless, design constraints such as “dark silicon” — where not all transistors can be activated simultaneously due to thermal limitations — remain a concern.

### *Cost and Yield Considerations*

Historically, cost per transistor declined with each successive node. However, at 5 nm and beyond, this trend has slowed or even reversed<sup>15</sup>. EUV lithography, increased process complexity, and reduced yield have significantly raised wafer costs, particularly at 3 nm. These cost pressures are driving a paradigm shift toward chiplet-based architectures.

Rather than producing a single monolithic die at the latest node, designers can partition functionality into smaller chiplets. Critical logic blocks can be fabricated at 3 nm, while less performance-sensitive blocks such as I/O and analog functions are implemented on mature nodes like 14 nm. These chiplets are then integrated via advanced packaging techniques, optimizing overall performance, yield, and cost<sup>13</sup>.

### 3D Heterogeneous Integration and Emerging Architectures

Beyond 2.5D chiplet integration, three-dimensional (3D) stacking is emerging as a key strategy for density scaling. Through-silicon vias (TSVs) and wafer-to-wafer bonding enable vertical stacking of dies, such as memory-on-logic or logic-on-logic configurations.

Of particular interest is the Complementary FET (CFET) architecture, where NMOS and PMOS transistors are stacked vertically rather than placed laterally<sup>22</sup>. This configuration doubles effective transistor density while maintaining CMOS functionality. CFETs can be realized by vertically stacking two GAAFETs using either silicon nanosheets or 2D materials. While early demonstrations confirm CFET feasibility, precise alignment and vertical interconnect formation remain formidable challenges.

Another novel approach is the Vertical Transport FET (VTFET), pioneered by IBM and others. In VTFETs, the current flows vertically from source to drain, and the gate wraps around a vertical channel. This configuration offers over  $2\times$  density improvements compared to planar transistors, with potential performance gains<sup>17</sup>.

Both CFET and VTFET architectures are still in the research and development phase but are being actively explored as potential successors to GAAFETs when lateral scaling saturates.

### Design-Technology Co-Optimization (DTCO) and System-Level Gains

The increasing complexity of advanced nodes necessitates design-technology co-optimization (DTCO). Designers must understand manufacturing constraints, while process engineers must provide levers (e.g., new devices, layout options) that designers can exploit. DTCO is critical to extracting maximum value from each technology generation.

Heterogeneous integration is increasingly viewed as the third pillar of progress, alongside device scaling and circuit-level innovation. System-level benefits such as reduced memory access latency and lower energy per operation can be achieved by vertically stacking memory and logic. Similarly, chiplet designs enable function-specific optimization across different process nodes, improving both performance-per-watt and performance-per-dollar.

Scaling to 3 nm and beyond is no longer just a matter of shrinking transistors. It requires multidisciplinary innovation across materials science (e.g., novel channels and dielectrics), electrical engineering (e.g., CFETs, VTFETs), and

computer architecture (e.g., chiplet systems, DTCO). Heterogeneous integration is now a cornerstone strategy for sustaining Moore's Law—allowing meaningful system-level advancements even when traditional transistor scaling slows. The next section will explore the broader implications of these developments on the future of semiconductor technology.

## 6. CONCLUSION AND OUTLOOK

Transistor scaling has reached a stage where geometric and material innovations are as essential as dimensional reduction. Gate-All-Around FETs (GAAFETs), notably nanosheet transistors, have demonstrated their viability at the 3 nm node, delivering improved performance and energy efficiency. This analysis confirms that GAAFETs outperform FinFETs in drive current, electrostatic control, and leakage, validating the industry's shift to GAAFETs for 3 nm and 2 nm technologies. Early deployments by Samsung and Intel further affirm GAAFETs as practical solutions for next-generation CMOS.

Looking ahead, several critical directions are emerging:

- *New Materials for Scaled Channels:* Two-dimensional (2D) semiconductors offer compelling properties—atomic-scale thickness, strong gate control, and reduced short-channel effects—that make them prime candidates for sub-2 nm technologies. Hybrid stacks, such as CFETs combining a silicon GAAFET and a 2D FET, may become a key architecture. High-mobility III-V compounds and strain-engineered SiGe are also under exploration for performance-critical applications like RF or analog blocks.

- *Beyond-GAAFET Device Architectures:* Vertical Transport FETs (VTFETs) and Complementary FETs (CFETs) extend scaling into the third dimension. VTFETs rotate the transistor vertically to improve density; CFETs vertically stack NMOS and PMOS to halve area. Lab demonstrations show promise<sup>17</sup>, but challenges in manufacturability and circuit reliability remain. These devices could succeed GAAFETs later this decade.

- *Heterogeneous Integration and System Co-design:* As transistor pitch scaling slows, progress continues through packaging and architectural co-design—the essence of "More-than-Moore." Future systems will leverage 2.5D and 3D integration, combining chiplets across nodes and technologies (logic, memory, photonics) within a single package. Success demands cross-disciplinary collaboration spanning materials, devices, circuits, and systems.

In summary, the sub-3 nm roadmap presents formidable challenges, but also vast potential. GAAFETs have opened a path forward for near-term scaling, while emerging materials and 3D device architectures promise long-term extension. Realizing this future will require synergy between device physics, fabrication technology, and system design. With continued collaboration between academia and industry, the momentum of Moore's Law can be sustained—powering breakthroughs in computing, communications, and beyond.

## REFERENCES

- Bohr M.T., Young I.A. CMOS Scaling Trends and Beyond, *IEEE Micro*, **2017**, *37*, 20–29.

- Saha S.K. FinFET Devices for VLSI Circuits and Systems, *CRC Press*, Boca Raton, 2020.

- Lin C., others. High performance 14 nm SOI FinFET CMOS technology with  $0.0174 \mu\text{m}^2$  embedded DRAM and 15 levels of Cu metallization, *Proc. IEDM*, 2014, p. 3.8.1–3.8.3.

- Wu S.-Y., others. A 16 nm FinFET CMOS technology for mobile SoC and computing applications, *Proc. IEDM*, 2013, p. 9.1.1–9.1.4.

- Karimi K., Fardoust A., Javanmard M. Comprehensive Review of FinFET Technology: History, Structure, Challenges, Innovations, and Emerging Sensing Applications, *Micromachines*, **2024**, *15*, 1187.

- Wong H., Kakushima K. On the Vertically Stacked Gate-All-Around Nanosheet and Nanowire Transistor Scaling beyond the 5 nm Technology Node, *Nanomaterials*, **2022**, *12*, 1748.

- Soma U. Transistor Evolution: A Comprehensive Overview from TFT to TFET and Beyond, *Proc. Natl. Acad. Sci. India Sect. Phys. Sci.*, 2025.

- Das R.R., Rajalekshmi T.R., James A. FinFET to GAA MBCFET: A Review and Insights, *IEEE Access*, **2024**, *12*, 50556–50577.

- Hu W., Li F. Scaling Beyond 7 nm Node: An Overview of Gate-All-Around FETs, *Proc. ISNE*, 2021, p. 1–6.

- Yoon J.-S., Jeong J., Lee S., Baek R. Optimization of nanosheet number and width of multi-stacked nanosheet FETs for sub-7-nm node system on chip applications, *Jpn. J. Appl. Phys.*, **2019**, *58*, 084505.

- Kim S., others. Investigation of Device Performance for Fin Angle Optimization in FinFET and Gate-All-Around FETs for 3 nm-Node and Beyond, *IEEE Trans. Electron Devices*, **2022**, *69*, 2088–2093.

- Barraud S., others. 7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing, *IEEE VLSI Technol. Symp.*, 2020, p. 1–2.

- Jeong J., Lee S.H., Masuoka S.-A., Min S., Lee S., Kim S., Myung T., Choi B., Sohn C.-W., Kim S.W., Choi J., Park J., Lee H., Kim T., Kim S., Yasuda-Masuoka Y., Ku J.-H., Jeong G. World's First GAA 3 nm Foundry platform Technology (SF3) with Novel Multi-Bridge-Channel-FET (MBCFET™) Process, *2023 IEEE Symp. VLSI Technol. Circuits*, 2023, p. 1–2.

- Maxey K., Naylor C.H., O'Brien K.P., Penumatcha A., Oni A., Mokhtarzadeh C., Dorow C.J., Rogan C., Holybee B., Tronic T., Adams D., Arefin N., Sen Gupta A., Lin C.-C., Zhong T., Lee S., Kitamura A., Bristol R., Clendenning S.B., Avci U., Metz M. 300 mm MOCVD 2D CMOS Materials for More (Than) Moore Scaling, *2022 IEEE Symp. VLSI Technol. Circuits*, 2022, p. 419–420.

- Chen S., Zhang H., Ling Z., Zhai J., Yu B. The Survey of 2.5D Integrated Architecture: An EDA perspective, *Proc. 30th Asia S. Pac. Des. Autom. Conf.*, Association for Computing Machinery, New York, NY, USA; 2025, p. 285–293.

- Joung S., Kim S. Leakage Performance Improvement in Multi-Bridge-Channel Field Effect Transistor (MBCFET) by Adding Core Insulator Layer, *2019 Int. Conf. Simul. Semicond. Process. Devices SISPAD*, 2019, p. 1–4.

- Abdelaziz L., Khaled B., Mustapha G. Comparative analysis of TG FinFET and GAA FinFET in 3 nm technology node, *2023 27th Int. Conf. Inf. Technol. IT*, 2023, p. 1–4.

- Wu S.-Y., Chang C.H., Chiang M.C., Lin C.Y., Liaw J.J., Cheng J.Y., Yeh J.Y., Chen H.F., Chang S.Y., Lai K.T., Liang M.S., Pan K.H., Chen J.H., Chang V.S., Luo T.C., Wang X., Mor Y.S., Lin C.I., Wang S.H., Hsieh M.Y., Chen C.Y., Wu B.F., Lin C.J., Liang C.S., Tsao C.P., Li C.T., Chen C.H., Hsieh C.H., Liu H.H., Chen P.N., Chen C.C., Chen R., Yeo Y.C., Chui C.O., Chang W., Lee T.L., Huang K.B., Lin H.J., Chen K.W., Tsai M.H., Chen K.S., Chen X.M., Cheng Y.K., Wang C.H., Shue W., Ku Y., Jang S.M., Cao M., Lu L.C., Chang T.S. A 3 nm CMOS FinFlex™ Platform Technology with Enhanced Power Efficiency and Performance for Mobile SoC and High Performance Computing Applications, *2022 Int. Electron Devices Meet. IEDM*, 2022, p. 27.5.1–27.5.4.

- Saini K., Kumar V. Comparative Analysis of 12 nm Gate-all-Around Vertically Stacked Nanosheet Field Effect Transistor for High-k Gate-oxide Dielectrics, *2024 First Int. Conf. Electron. Commun. Signal Process. ICECSP*, 2024, p. 1–6.

20. Eun Shim D., Kumar P., Ashok Kini A., Mallikarjuna M., Nahid Haque Shazon Md., Naeemi A. GT3: An Open-Source 3 nm GAAFET PDK and Platform for End-to-End Evaluation of Emerging Technologies, *IEEE Trans. Electron Devices*, **2025**, 72, 1582–1588.

21. Scognamiglio L., Mo F., Spano C.E., Vacca M., Piccinini G. Simulation Study on the Impact of Miniaturization in 3 nm Node 3D Junctionless Transistors, *IEEE Trans. Nanotechnol.*, **2025**, 24, 102–109.

22. Wang D., others. Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node, *Electronics*, **2023**, 12, 0770.

23. Ma M., Li C., Ma J., Yang W., Li H., You H., Deen M.J. Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET, *Electronics*, **2025**, 14, 1091.

24. Zhu C., Zhu X., Yu S., Wei Zhang D. Process-Dependent Evolution of Channel Stress and Stress-Induced Mobility Gain in FinFET, Normal GAAFET, and Si/SiGe Hybrid Channel GAAFET, *IEEE Access*, **2025**, 13, 21600–21609.

25. Wang X., Kim Y., Baek G.H., Bannore K.G., Dave K., Joushaghani A., Kang N., Ko M., Pillai A.M., Prakash Movva H.C., Park G., Rahman M., Subramaniam S., Vashishta V., Yang T., Guo Z., Karl E.A. 29.2 Å 0.021  $\mu\text{m}^2$  High-Density SRAM in Intel-18A-RibbonFET Technology with PowerVia-Backside Power Delivery, *2025 IEEE Int. Solid-State Circuits Conf. ISSCC*, **2025**, vol. 68, p. 494–496.

26. Agrawal A., Chakraborty W., Li W., Ryu H., Markman B., Hoon S.H., Paul R.K., Huang C.Y., Choi S.M., Rho K., Shu A., Iglesias R., Wallace P., Ghosh S., Cheong K.L., Hockel J.L., Thorman R., Baumgartel L., Shoer L., Mishra V., Berrada S., Ashita A., Weber C., Obradovic B., Oni A.A., Brooks Z., Franco N., Kavalieros J., Dewey G. Silicon RibbonFET CMOS at 6 nm Gate Length, *2024 IEEE Int. Electron Devices Meet. IEDM*, **2024**, p. 1–4.

27. Hafez W., Agnihotri P., Asoro M., Aykol M., Bains B., Bambury R., Bapna M., Barik A., Chatterjee A., Chiu P.C., Chu T., Firby C., Fischer K., Fradkin M., Greve H., Gupta A., Haralson E., Haran M., Hicks J., Illa A., Jang M., Klopcic S., Koprinsky M., Kuns B., Lai H.-h., Lanni G., Lee S.-H., Lindert N., Lo C.-l., Luo Y., Malyavanatham G., Marinkovic B., Maymon Y., Nabors M., Neirynck J., Packan P., Paliwal A., Pantisano L., Paulson L., Penmatsa P., Prasad C., Puls C., Rahman T., Ramaswamy R., Samant S., Sell B., Sethi K., Shah F., Shamanna M., Shang K., Li Q., Sibakoti M., Stoeger J., Strutt N., Thirugnanasambandam R., Tsai C., Wang X., Wang A., Wu S.-j., Xu Q., Zhong X.-h., Natarajan S. Intel PowerVia Technology: Backside Power Delivery for High Density and High-Performance Computing, *2023 IEEE Symp. VLSI Technol. Circuits*, **2023**, p. 1–2.

28. Chen Y., Sankatali V., Mishra S., Ryckaert J., Myers J., Biswas D. Thermal Implications in Scaling High-Performance Server 3D Chiplet-Based 2.5D SoC from FinFET to Nanosheet, *2024 IEEE Comput. Soc. Annu. Symp. VLSI ISVLSI*, **2024**, p. 45–50.

29. Loubet N., Hook T., Montanini P., Yeung C.-W., Kanakasabapathy S., Guillom M., Yamashita T., Zhang J., Miao X., Wang J., Young A., Chao R., Kang M., Liu Z., Fan S., Hamieh B., Sieg S., Mignot Y., Xu W., Seo S.-C., Yoo J., Mochizuki S., Sankarapandian M., Kwon O., Carr A., Greene A., Park Y., Frougier J., Galatage R., Bao R., Shearer J., Conti R., Song H., Lee D., Kong D., Xu Y., Arceo A., Bi Z., Xu P., Muthinti R., Li J., Wong R., Brown D., Oldiges P., Robison R., Arnold J., Felix N., Skordas S., Gaudiello J., Standaert T., Jagannathan H., Corliss D., Na M.-H., Knorr A., Wu T., Gupta D., Lian S., Divakaruni R., Gow T., Labelle C., Lee S., Paruchuri V., Bu H., Khare M. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET, *2017 Symp. VLSI Technol.*, **2017**, p. T230–T231.

30. Knobloch T., Uzlu B., Illarionov Y.Yu., Wang Z., Otto M., Filipovic L., Waltl M., Neumaier D., Lemme M.C., Grasser T. Improving stability in two-dimensional transistors with amorphous gate oxides by Fermi-level tuning, *Nat. Electron.*, **2022**, 5, 356–366.

31. Shen P.-C., Su C., Lin Y., Chou A.-S., Cheng C.-C., Park J.-H., Chiu M.-H., Lu A.-Y., Tang H.-L., Tavakoli M.M., Pitner G., Ji X., Cai Z., Mao N., Wang J., Tung V., Li J., Bokor J., Zettl A., Wu C.-I., Palacios T., Li L.-J., Kong J. Ultralow contact resistance between semimetal and monolayer semiconductors, *Nature*, **2021**, 593, 211–217.

32. Kwak K., Yoon H., Hong S., Kang B.H. Advances in 2D Molybdenum Disulfide Transistors for Flexible and Wearable Electronics, *Micromachines*, **2024**, 15, 1476.

33. Chou B.-J., Chung Y.-Y., Yun W.-S., Hsu C.-F., Li M.-Y., Su S.-K., Liew S.-L., Hou V.D.-H., Chen C.-W., Kei C.-C., Shen Y.-Y., Chang W.-H., Lee T.Y., Cheng C.-C., Radu I.P., Chien C.-H. High-performance monolayer MoS<sub>2</sub> nanosheet GAA transistor, *Nanotechnology*, **2024**, 35, 125204.

34. Mortelmans W., Buragohain P., Rogan C., Kitamura A., Dorow C.J., O'Brien K.P., Ramamurthy R., Lux J., Zhong T., Harlson S., Gillispie E., Wilson T., Oni A., Penumatcha A., Kavrik M., Maxey K., Kozhakhmetov A., Lin C.-C., Lee S., Avci U. Record Performance in GAA 2D NMOS and PMOS Using Monolayer MoS<sub>2</sub> and WSe<sub>2</sub> with Scaled Contact and Gate Length,

35. Totorica N, Hu W, Li F. Simulation of different structured gate-all-around FETs for 2 nm node. *Eng Res Express*, **2024**;6:035326.